# **AMD64 Virtualization Technology**

# **Secure Virtual Machine Architecture Reference Manual**

Publication No. Revision Date

33047 3.02 **December 2005**  © 2005 Advanced Micro Devices, Inc. All rights reserved.

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

#### **Trademarks**

AMD, the AMD Arrow logo, AMD Athlon, AMD Opteron, and combinations thereof, are trademarks, and AMD-K6 is a registered trademark of Advanced Micro Devices, Inc.

HyperTransport is a licensed trademark of the HyperTransport Technology Consortium.

Pentium is a registered trademark of Intel Corporation.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

## **Contents**

| Revis | Revision History |                                                                                                                                                                                                                                                                                                        |                                              |

|-------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Prefa |                  |                                                                                                                                                                                                                                                                                                        |                                              |

| 1     | Intro            | duction                                                                                                                                                                                                                                                                                                | 1                                            |

|       | 1.1 1.2          | The Virtual Machine Monitor SVM Hardware Overview. Virtualization Support Guest Mode External Access Protection Tagged TLB Interrupt Support Intercepting physical interrupt delivery Virtual interrupts Sharing a physical APIC. Restartable Instructions Security Support Attestation. Memory Clear. | .1<br>.2<br>.2<br>.2<br>.2<br>.2<br>.2<br>.2 |

| 2     | SVM              | Processor and Platform Extensions                                                                                                                                                                                                                                                                      |                                              |

|       | 2.1 2.2          | Enabling SVM  VMRUN Instruction  Basic Operation  Saving Host State  Loading Guest State  Control Bits  Segment State in the VMCB  Canonicalization and Consistency Checks  VMRUN and TF/RF bits in EFLAGS                                                                                             | .5<br>.6<br>.7<br>.7<br>.8<br>.9             |

|       | 2.3 2.4          | #VMEXIT Intercept Operation Exception intercepts Instruction intercepts State Saved on Exit Intercepts During IDT Interrupt Delivery EXITINTINFO Pseudo-Code                                                                                                                                           | 12<br>13<br>13<br>14<br>14<br>14<br>16       |

|       | 2.5              | Instruction Intercepts                                                                                                                                                                                                                                                                                 | 17<br>17<br>17<br>17<br>18                   |

Contents

|     | RDTSC Instruction Intercept   |    |

|-----|-------------------------------|----|

|     | RDPMC Instruction Intercept   | 18 |

|     | PUSHF Instruction Intercept   | 18 |

|     | POPF Instruction Intercept    | 18 |

|     | CPUID Instruction Intercept   | 18 |

|     | RSM Instruction Intercept     | 19 |

|     | IRET Instruction Intercept    | 19 |

|     | Software Interrupt Intercept  | 19 |

|     | INVD Instruction Intercept    |    |

|     | PAUSE Instruction Intercept   | 19 |

|     | HLT Instruction Intercept     | 19 |

|     | INVLPG Instruction Intercept  | 19 |

|     | INVLPGA Instruction Intercept | 19 |

|     | VMRUN Instruction Intercept   | 19 |

|     | VMLOAD Instruction Intercept  | 19 |

|     | VMSAVE Instruction Intercept  | 20 |

|     | VMMCALL Instruction Intercept | 20 |

|     | STGI Instruction Intercept    | 20 |

|     | CLGI Instruction Intercept    | 20 |

|     | SKINIT Instruction Intercept  |    |

|     | RDTSCP Instruction Intercept  | 20 |

|     | ICEBP Instruction Intercept   | 20 |

|     | WBINVD Instruction Intercept  |    |

| 2.6 | IOIO Intercepts               | 20 |

|     | I/O Permissions Map           |    |

|     | IN and OUT Behavior           |    |

|     | I/O Intercept Information     |    |

| 2.7 | MSR Intercepts                |    |

|     | MSR Permissions Map           |    |

|     | RDMSR and WRMSR Behavior      |    |

|     | MSR Intercept Information     |    |

| 2.8 | Exception Intercepts          |    |

|     | Example:                      |    |

|     | #DE (Divide By Zero)          |    |

|     | #DB (Debug)                   |    |

|     | Vector 2 (Reserved)           |    |

|     | #BP (Breakpoint)              |    |

|     | #OF (Overflow)                |    |

|     | #BR (Bound-Range)             |    |

|     | #UD (Invalid Opcode)          |    |

|     | #NM (Device-Not-Available)    |    |

|     | #DF (Double Fault)            |    |

|     | Vector 9 (Reserved)           |    |

|     | #TS (Invalid TSS)             |    |

|     | #NP (Segment Not Present)     |    |

|     | #SS (Stack Fault)             |    |

|     | #GP (General Protection)      | 26 |

|      | #PF (Page Fault)                                  | 26 |

|------|---------------------------------------------------|----|

|      | #MF (X87 Floating Point)                          |    |

|      | #AC (Alignment Check)                             |    |

|      | #MC (Machine Check)                               |    |

|      | #XF (SIMD Floating Point)                         |    |

| 2.9  | Interrupt Intercepts                              |    |

|      | INTR Intercept                                    |    |

|      | NMI Intercept                                     | 27 |

|      | SMI Intercept                                     | 27 |

|      | INIT Intercept                                    | 27 |

|      | Virtual Interrupt Intercept                       | 27 |

| 2.10 | Miscellaneous Intercepts                          | 27 |

|      | Task Switch Intercept                             | 27 |

|      | Ferr_Freeze Intercept                             |    |

|      | Shutdown Intercept                                |    |

| 2.11 | VMSAVE and VMLOAD Instructions                    | 28 |

| 2.12 | TLB Control                                       |    |

|      | Software Rule                                     |    |

|      | TLB Flush                                         |    |

|      | Invalidate Page, Alternate ASID                   |    |

| 2.13 | Global Interrupt Flag, STGI and CLGI Instructions |    |

| 2.14 | VMMCALL Instruction                               |    |

| 2.15 | Paged Real Mode                                   |    |

| 2.16 | Event Injection                                   |    |

| 2.17 | Interrupt and localAPIC Support                   |    |

|      | Physical (INTR) Interrupt Masking in EFLAGS       |    |

|      | Virtualizing APIC.TPR                             |    |

|      | TPR Access in 32-bit Mode                         |    |

|      | Injecting Virtual (INTR) Interrupts               |    |

|      | Interrupt Shadows                                 |    |

|      | Virtual Interrupt Intercept                       |    |

|      | Interrupt Masking in LocalAPIC                    |    |

|      | NMI Support                                       |    |

| 2.18 | SMM Support                                       |    |

| 2.10 | Sources of SMI                                    |    |

|      | Response to SMI                                   |    |

|      | Containerizing Platform SMM                       |    |

|      | Advanced Support                                  |    |

| 2.19 | Last Branch Record Virtualization                 |    |

| 2.13 | Enabling LBR Virualization                        |    |

|      | Host and Guest LBR Virtualization                 |    |

|      | LBR Virtualization CPUID Feature Detection        |    |

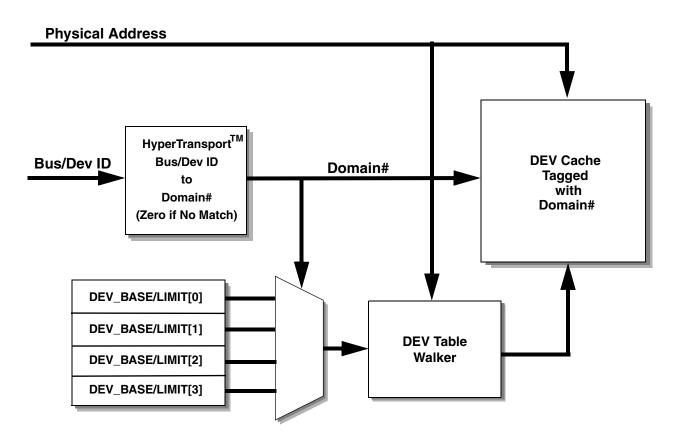

| 2.20 | External Access Protection                        |    |

|      | Device IDs and Protection Domains                 |    |

|      | Device Exclusion Vector (DEV)                     |    |

|      | Host Bridge and Processor DEV Caching             |    |

|      | _                                                 |    |

Contents v

|   |       | Multiprocessor Issues                                  | 44 |

|---|-------|--------------------------------------------------------|----|

|   |       | Access Checking                                        | 44 |

|   |       | Memory Space Accesses                                  | 44 |

|   |       | I/O Space Accesses                                     | 44 |

|   |       | Config Space Accesses                                  | 45 |

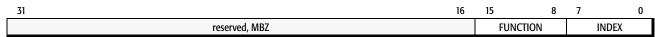

|   |       | DEV Capability Block                                   | 45 |

|   |       | DEV Capability Header                                  | 46 |

|   |       | DEV Register Access Mechanism                          |    |

|   |       | DEV Control and Status Registers                       |    |

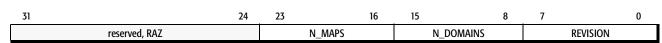

|   |       | DEV_CAP Register                                       |    |

|   |       | DEV_CR Register                                        | 48 |

|   |       | DEV_BASE Address/Limit Registers                       | 48 |

|   |       | DEV_MAP Registers                                      |    |

|   |       | Unauthorized Access Logging                            |    |

|   |       | Secure Initialization Support                          |    |

|   | 2.21  | Nested Paging Facility                                 |    |

|   |       | Traditional Paging versus Nested Paging                |    |

|   |       | Replicated State                                       |    |

|   |       | Enabling Nested Paging                                 |    |

|   |       | Nested Paging and VMRUN/#VMEXIT                        |    |

|   |       | Nested Table Walk                                      |    |

|   |       | Host versus Guest Page Faults, Fault Ordering          |    |

|   |       | Combining Host and Guest Attributes                    | 55 |

|   |       | Combining Memory Types, MTRRs                          |    |

|   |       | Memory Consistency Issues                              |    |

|   |       | Page Splintering                                       |    |

|   |       | Legacy PAE Mode                                        |    |

|   |       | A20 Masking                                            |    |

|   |       | Detecting Nested Paging Support                        |    |

| 3 | Secur | rity                                                   |    |

| J | Secui | •                                                      |    |

|   |       | SKINIT Instruction                                     |    |

|   |       | Automatic Memory Clearing                              |    |

|   |       | Security Exception                                     |    |

|   | 3.1   | Secure Startup with SKINIT                             | 61 |

|   |       | Secure Loader                                          |    |

|   |       | Secure Loader Image                                    |    |

|   |       | Secure Loader Block                                    |    |

|   |       | Trusted Platform Module                                |    |

|   |       | System Interface, Memory Controller and I/O Hub Logic. |    |

|   |       | SKINIT Operation                                       |    |

|   |       | Pending interrupts                                     |    |

|   |       | Debug considerations                                   |    |

|   |       | SL Abort                                               |    |

|   |       | Secure Multiprocessor Initialization                   |    |

|   |       | Software requirements for Secure MP initialization .   |    |

|   |       | AP Startup Sequence                                    |    |

|   |       | Pending interrupts                                     | 68 |

|   |       |                                                        |    |

|     |         | Aborting MP initialization          | 8 |

|-----|---------|-------------------------------------|---|

|     | 3.2     | Automatic Memory Clear              |   |

|     | 3.3     | Security Exception (#SX)7           | C |

| 4   | SVM     | Instruction Set Reference 7         | 1 |

|     | 4.1     | Changes to RSM Instruction          | 1 |

|     | 4.2     | New Instructions                    |   |

|     |         | CLGI                                | 2 |

|     |         | INVLPGA                             |   |

|     |         | MOV (CRn)                           |   |

|     |         | SKINIT                              |   |

|     |         | STGI                                |   |

|     |         | VMLOAD                              |   |

|     |         | VMMCALL8                            | C |

|     |         | VMRUN                               | 1 |

|     |         | VMSAVE8                             |   |

| App | endix A | A Reset Values and INIT             | 9 |

| App | endix l | B Processor Feature Identification9 | 1 |

| App | endix ( | C Layout of VMCB 9                  | 3 |

| App | endix l | D Intercept Exit Codes              | 3 |

| App | endix l | E New and Changed MSRs 10           | 7 |

Contents vii

33047-Rev. 3.02-December 2005

viii Contents

## **List of Figures**

| Figure 2-1. | EXITINTINFO for All Intercepts                                                 |

|-------------|--------------------------------------------------------------------------------|

| Figure 2-2. | EXITINFO1 for IOIO Intercept21                                                 |

| Figure 2-3. | EVENTINJ Field in the VMCB33                                                   |

| Figure 2-4. | Format of SEOI register (in localAPIC)37                                       |

| Figure 2-5. | Host Bridge DMA Checking45                                                     |

| Figure 2-7. | Format of DEV_CAP Register (in PCI Config Space) 48                            |

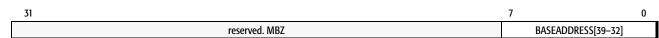

| Figure 2-8. | Format of DEV_BASE_HI[n] Registers                                             |

| Figure 2-9. | Format of DEV_BASE_LO[n] Registers49                                           |

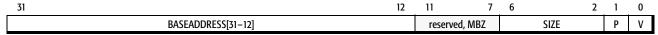

| Figure 2-10 | .Format of DEV_MAP[n] Registers49                                              |

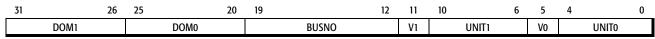

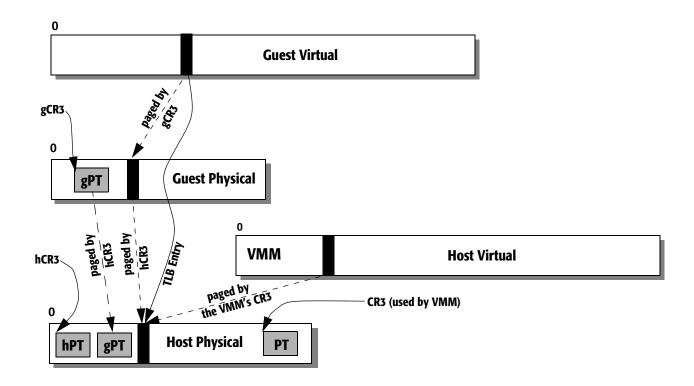

| Figure 2-11 | .Address Translation with Traditional Paging51                                 |

| Figure 2-12 | .Address Translation with Nested Paging                                        |

| Figure 3-1. | SLB Example Layout                                                             |

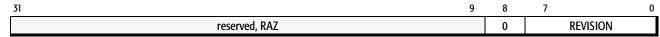

| Figure B-1. | SVM Revision and Feature Identification in EAX, Extended Function 8000_000Ah   |

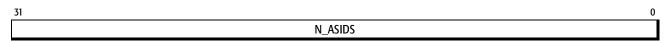

| Figure B-2. | SVM Revision and Feature Identification in EBX, Extended Function 8000_000Ah91 |

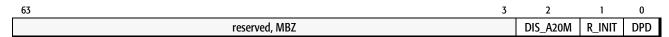

| Figure B-3. | SVM Revision and Feature Identification in EDX, Extended Function 8000_000Ah91 |

| Figure E-1. | Layout of VM_CR MSR (C001_0114h)107                                            |

| Figure E-2. | Layout of SMM_CTL MSR (C001_0116h)108                                          |

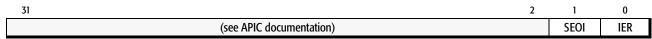

| Figure E-3. | Extended APIC feature register                                                 |

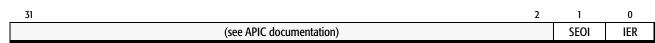

| Figure E-4. | Extended APIC control register                                                 |

List of Figures ix

33047-Rev. 3.02-December 2005

x List of Figures

## **List of Tables**

| Table 2-1.  | Guest Exception or Interrupt Types                            |

|-------------|---------------------------------------------------------------|

| Table 2-2.  | Ranges of MSR Permissions Map23                               |

| Table 2-3.  | Effect of the GIF on Interrupt Handling                       |

| Table 2-4.  | Guest Exception or Interrupt Types33                          |

| Table 2-5.  | INIT Handling in Different Operating Modes38                  |

| Table 2-6.  | NMI Handling in Different Operating Modes                     |

| Table 2-7.  | SMI Handling in Different Operating Modes 40                  |

| Table 2-8.  | DEV Capability Block, Overall Layout46                        |

| Table 2-9.  | DEV Capability Header (DEV_HDR) (in PCI Config Space) $$ . 46 |

| Table 2-10. | Encoding of function field in DEV_OP register                 |

| Table 2-11. | DEV_CR Control Register48                                     |

| Table 2-12. | Combining Guest and Host PAT Types                            |

| Table 2-13. | Combining PAT and MTRR Types                                  |

| Table C-1.  | VMCB Layout, Control Area93                                   |

| Table C-2.  | VMCB Layout, State Save Area99                                |

| Table D-1.  | SVM Intercept Codes                                           |

| Table E-1.  | SVM New MSRs                                                  |

| Table E-2.  | Secure-VM localAPIC Registers                                 |

List of Tables xi

33047-Rev. 3.02-December 2005

xii List of Tables

## **Revision History**

| Date          | Revision | Description                                                                                                                                                                                                            |

|---------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| December 2005 | 3.02     | Added documentation of LBR virtualization in Section 2.19 and the VMCB layout tables in Appendix B; Updated documentation of nested paging in Section 2.21; Converted SVM intercept codes in Table D-1 to hexadecimal. |

| May 2005      | 3.01     | Corrected factual errors in Section 2.21.13, "Other Guest Attributes," on page 61.                                                                                                                                     |

| April 2005    | 3.00     | First Public Release.                                                                                                                                                                                                  |

Revision History xiii

33047-Rev. 3.02-December 2005

xiv Revision History

## **Preface**

### **About This Book**

This book describes the AMD64 technology Security and Virtual Machine (SVM) architecture, software requirements, instruction set extensions, changes to existing instructions, and new bit settings in system registers.

#### **Audience**

This volume is intended for programmers writing virtual machine monitor software and other SVM applications or system utilities. It assumes an understanding of AMD64 architecture application-level and system-level programming as described in Volumes 1 and 2 of the AMD64 Architecture Programmer's Manual (order# 24592 and order# 24593).

This volume describes SVM architecture resources and functions that are managed by system software, including operating-mode control, memory management, intercepts, interrupts and exceptions, state-change management, systemmanagement mode, and processor initialization, as well as extensions to the AMD64 instruction set that are used to operate on SVM data structures.

Preface xv

## **Organization**

This volume begins with an overview of SVM, followed by chapters that describe the following details of system programming:

- System Resources—The data structures, system registers, software responsibilities, and hardware support to implement SVM systems.

- *SVM Instruction Set*—The extensions to the AMD64 instruction set used to control SVM operations.

The appendices describe details of model-specific registers (MSRs) and data strucure layout. Definitions assumed throughout this volume are listed below. The index at the end of this volume cross-references topics within the volume. For other topics relating to the AMD64 architecture, see the tables of contents and indices of the references given in "Related Documents" on page xxv.

### **Definitions**

Some of the following definitions assume a knowledge of the legacy x86 architecture. See "Related Documents" on page xxv for descriptions of the legacy x86 architecture.

#### **Terms and Notation**

1011b

A binary value—in this example, a 4-bit value.

F0EAh

A hexadecimal value—in this example a 2-byte value.

[1,2)

A range that includes the left-most value (in this case, 1) but excludes the right-most value (in this case, 2).

7:4

A bit range, from bit 7 to 4, inclusive. The high-order bit is shown first.

32-bit mode

Legacy mode or compatibility mode in which a 32-bit address size is active. See *legacy mode* and *compatibility mode*.

**xvi** Preface

#### 64-bit mode

A submode of *long mode*. In 64-bit mode, the default address size is 64 bits and new features, such as register extensions, are supported for system and application software.

#### #GP(0)

Notation indicating a general-protection exception (#GP) with error code of 0.

#### absolute

A displacement that references the base of a code segment rather than an instruction pointer. Contrast with *relative*.

#### **ASID**

Address space identifier.

#### byte

Eight bits.

#### clear

To write a bit value of 0. Compare set.

#### compatibility mode

A submode of *long mode*. In compatibility mode, the default address size is 32 bits, and legacy 16-bit and 32-bit applications run without modification.

#### CPL

Current privilege level.

#### CR0-CR4

A register range, from register CR0 through CR4, inclusive, with the low-order register first.

#### CR0.PE = 1

Notation indicating that the PE bit of the CR0 register has a value of 1.

#### displacement

A signed value that is added to the base of a segment (absolute addressing) or an instruction pointer (relative addressing). Same as *offset*.

#### doubleword

Two words, or four bytes, or 32 bits.

Preface xvii

#### double quadword

Eight words, or 16 bytes, or 128 bits. Also called *octword*.

#### DS:rSI

The contents of a memory location whose segment address is in the DS register and whose offset relative to that segment is in the rSI register.

#### EFER.LME = 0

Notation indicating that the LME bit of the EFER register has a value of 0.

#### effective address size

The address size for the current instruction after accounting for the default address size and any address-size override prefix.

### effective operand size

The operand size for the current instruction after accounting for the default operand size and any operand-size override prefix.

#### element

See vector.

#### exception

An abnormal condition that occurs as the result of executing an instruction. The processor's response to an exception depends on the type of the exception. Control is transferred to the handler (or service routine) for that exception, as defined by the exception's vector. When unmasked, the exception handler is called, and when masked, a default response is provided instead of calling the handler.

#### FF/0

Notation indicating that FF is the first byte of an opcode, and a subopcode in the ModR/M byte has a value of 0.

#### flush

An often ambiguous term meaning (1) writeback, if modified, and invalidate, as in "flush the cache line," or (2) invalidate, as in "flush the pipeline," or (3) change a value, as in "flush to zero."

**xviii** Preface

**GIF**

Global interrupt flag.

GDT

Global descriptor table.

IDT

Interrupt descriptor table.

IGN

Ignore. Field is ignored.

IVT

The real-address mode interrupt-vector table.

LDT

Local descriptor table.

long mode

An operating mode unique to the AMD64 architecture. A processor implementation of the AMD64 architecture can run in either *long mode* or *legacy mode*. Long mode has two submodes, *64-bit mode* and *compatibility mode*.

lsb

Least-significant bit.

LSB

Least-significant byte.

main memory

Physical memory, such as RAM and ROM (but not cache memory) that is installed in a particular computer system.

mask

A field of bits used for a control purpose.

**MBZ**

Must be zero. If software attempts to set an MBZ bit to 1, a general-protection exception (#GP) occurs.

memory

Unless otherwise specified, main memory.

msb

Most-significant bit.

Preface xix

**MSB**

Most-significant byte.

octword

Same as double quadword.

offset

Same as displacement.

PAE

Physical-address extensions.

physical memory

Actual memory, consisting of main memory and cache.

probe

A check for an address in a processor's caches or internal buffers. *External probes* originate outside the processor, and *internal probes* originate within the processor.

protected mode

A submode of legacy mode.

quadword

Four words, or eight bytes, or 64 bits.

RAZ

Read as zero (0), regardless of what is written.

real-address mode

See real mode.

real mode

A short name for real-address mode, a submode of legacy mode.

relative

A displacement (also called offset) from an instruction pointer rather than the base of a code segment. Contrast with *absolute*.

reserved

Fields marked as reserved may be used at some future time.

xx Preface

To preserve compatibility with future processors, reserved fields require special handling when read or written by software.

Reserved fields may be further qualified as MBZ, RAZ, SBZ or IGN (see definitions).

Software must not depend on the state of a reserved field, nor upon the ability of such fields to return to a previously written state.

If a reserved field is not marked with one of the previous qualifiers, software must not change the state of that field; it must reload that field with the same values returned from a prior read.

#### **REX**

An instruction prefix that specifies a 64-bit operand size and provides access to additional registers.

#### SBZ

Should be zero. It is the responsibility of software to set SBZ bits to zero. The result of setting an SBZ bit to 1 may be unpredictable.

#### set

To write a bit value of 1. Compare *clear*.

#### sticky bit

A bit that is set or cleared by hardware and that remains in that state until explicitly changed by software.

#### **TSS**

Task-state segment.

#### vector

An index into an interrupt descriptor table (IDT), used to access exception handlers. Compare *exception*.

#### virtual-8086 mode

A submode of *legacy mode*.

#### **VMCB**

Virtual machine control block.

#### VMM

Virtual machine monitor.

Preface xxi

word

Two bytes, or 16 bits.

*x*86

See legacy x86.

#### **Registers**

In the following list of registers, the names are used to refer either to a given register or to the contents of that register:

#### AH-DH

The high 8-bit AH, BH, CH, and DH registers. Compare *AL-DL*.

#### AL-DL

The low 8-bit AL, BL, CL, and DL registers. Compare AH–DH.

#### *AL-r15B*

The low 8-bit AL, BL, CL, DL, SIL, DIL, BPL, SPL, and R8B-R15B registers, available in 64-bit mode.

#### BP

Base pointer register.

#### CRn

Control register number *n*.

#### CS

Code segment register.

#### eAX-eSP

The 16-bit AX, BX, CX, DX, DI, SI, BP, and SP registers or the 32-bit EAX, EBX, ECX, EDX, EDI, ESI, EBP, and ESP registers. Compare *rAX-rSP*.

#### EBP

Extended base pointer register.

#### **EFER**

Extended features enable register.

#### **eFLAGS**

16-bit or 32-bit flags register. Compare *rFLAGS*.

#### **EFLAGS**

32-bit (extended) flags register.

**xxii** Preface

eIP

16-bit or 32-bit instruction-pointer register. Compare *rIP*.

**EIP**

32-bit (extended) instruction-pointer register.

**FLAGS**

16-bit flags register.

**GDTR**

Global descriptor table register.

**GPRs**

General-purpose registers. For the 16-bit data size, these are AX, BX, CX, DX, DI, SI, BP, and SP. For the 32-bit data size, these are EAX, EBX, ECX, EDX, EDI, ESI, EBP, and ESP. For the 64-bit data size, these include RAX, RBX, RCX, RDX, RDI, RSI, RBP, RSP, and R8–R15.

**IDTR**

Interrupt descriptor table register.

IP

16-bit instruction-pointer register.

**LDTR**

Local descriptor table register.

**MSR**

Model-specific register.

r8-r15

The 8-bit R8B-R15B registers, or the 16-bit R8W-R15W registers, or the 32-bit R8D-R15D registers, or the 64-bit R8-R15 registers.

rAX-rSP

The 16-bit AX, BX, CX, DX, DI, SI, BP, and SP registers, or the 32-bit EAX, EBX, ECX, EDX, EDI, ESI, EBP, and ESP registers, or the 64-bit RAX, RBX, RCX, RDX, RDI, RSI, RBP, and RSP registers. Replace the placeholder r with nothing for 16-bit size, "E" for 32-bit size, or "R" for 64-bit size.

Preface xxiii

```

RAX

```

64-bit version of the EAX register.

#### RAZ

Read as zero (0), regardless of what is written.

#### RBP

64-bit version of the EBP register.

#### RBX

64-bit version of the EBX register.

#### RCX

64-bit version of the ECX register.

#### RDI

64-bit version of the EDI register.

#### RDX

64-bit version of the EDX register.

#### rFLAGS

16-bit, 32-bit, or 64-bit flags register. Compare RFLAGS.

#### **RFLAGS**

64-bit flags register. Compare *rFLAGS*.

#### rIP

16-bit, 32-bit, or 64-bit instruction-pointer register. Compare *RIP*.

#### RIP

64-bit instruction-pointer register.

#### RSI

64-bit version of the ESI register.

#### RSP

64-bit version of the ESP register.

#### SP

Stack pointer register.

#### SS

Stack segment register.

**xxiv** Preface

TPR

Task priority register (CR8), a new register introduced in the AMD64 architecture to speed interrupt management.

TR

Task register.

#### **Endian Order**

The x86 and AMD64 architectures address memory using littleendian byte-ordering. Multibyte values are stored with their least-significant byte at the lowest byte address, and they are illustrated with their least significant byte at the right side. Strings are illustrated in reverse order, because the addresses of their bytes increase from right to left.

### **Related Documents**

- *AMD64 Architecture Programmer's Manual Volume 1: Application Programming*, order# 24592.

- AMD64 Architecture Programmer's Manual Volume 2: System Programming, order# 24593.

- AMD64 Architecture Programmer's Manual Volume 3: General Purpose and System Instructions, order# 24594.

Preface xxv

33047-Rev. 3.02-December 2005

**xxvi** Preface

## 1 Introduction

AMD security and virtual machine (SVM) architecture is designed to provide enterprise-class server virtualization software technology that facilitates virtualization development and deployment. An SVM enabled virtual machine architecture should provide hardware resources that allow a single machine to run multiple operating systems efficiently, while maintaining secure, resource-guaranteed isolation.

### 1.1 The Virtual Machine Monitor

A virtual machine monitor (VMM, also known as a hypervisor) consists of software that controls the execution of multiple guest operating systems on a single physical machine; the VMM provides each guest the appearance of full control over a complete computer system (memory, CPU, and all peripheral devices). The use of the term host refers to the execution context of the VMM. World switch refers to the operation of switching between the host and guest.

Fundamentally, VMMs work by *intercepting* and emulating in a safe manner sensitive operations in the guest (such as changing the page tables, which could give a guest access to memory it is not allowed to access). AMD's SVM provides hardware assists to improve performance and facilitate implementation of virtualization.

### 1.2 SVM Hardware Overview

SVM processor support provides a set of hardware extensions designed to enable economical and efficient implementation of virtual machine systems. Generally speaking, hardware support falls into two complementary categories: *virtualization* support and *security* support.

## 1.2.1 Virtualization Support

The AMD virtual machine architecture is designed to provide:

- Mechanisms for fast world switch between VMM and guest

- The ability to intercept selected instructions or events in the guest

- External (DMA) access protection for memory.

- Assists for interrupt handling and virtual interrupt support

- A guest/host tagged TLB to reduce virtualization overhead.

#### 1.2.2 Guest Mode

This new processor mode is entered through the VMRUN instruction. When in guest mode, the behavior of some x86 instructions changes to facilitate virtualization.

## 1.2.3 External Access Protection

Guests may be granted direct access to selected I/O devices. Hardware support is designed to prevent devices owned by one guest from accessing memory owned by another guest (or the VMM).

#### 1.2.4 Tagged TLB

In the SVM usage model, the VMM is mapped in a different address space than the guest. To reduce the cost of world switches, the TLB is tagged with an address space identifier (ASID) distinguishing host-space entries from guest-space entries.

## 1.2.5 **Interrupt Support**

To facilitate efficient virtualization of interrupts, the following support is provided under control of VMCB flags:

**Intercepting physical interrupt delivery.** The VMM can request that physical interrupts cause a running guest to exit, allowing the VMM to process the interrupt.

**Virtual interrupts.** The VMM can inject virtual interrupts into the guest. Under control of the VMM, a virtual copy of the EFLAGS.IF interrupt mask bit, and a virtual copy of the APIC's task priority register are used transparently by the guest instead of the physical resources.

**Sharing a physical APIC.** SVM allows multiple guests to share a physical APIC while guarding against malicious or defective guests that might leave high-priority interrupts unacknowledged forever (and thus shut out other guest's interrupts).

## 1.2.6 Restartable Instructions

SVM is designed to safely restart, with the exception of task switches, any intercepted instruction after the intercept. Instructions are either atomic or idempotent.

#### 1.2.7 **Security Support**

To further enable secure initialization SVM provides additional System support.

**Attestation.** The SKINIT instruction and associated system support (the Trusted Platform Module, or TPM) allow for verifiable startup of trusted software (such as a VMM), based on secure hash comparison.

**Memory Clear.** Automatic memory clear erases the contents of system memory on reset to prevent simple reset-based attacks on secrets stored in memory.

33047-Rev. 3.02-December 2005

## 2 SVM Processor and Platform Extensions

This chapter describes the operation of the SVM hardware extensions. These extensions can be grouped into the following categories:

- State switch—VMRUN, VMSAVE, VMLOAD instructions, global interrupt flag (GIF), and instructions to manipulate the latter (STGI, CLGI). ("VMRUN Instruction" on page 5, "VMSAVE and VMLOAD Instructions" on page 29, "Global Interrupt Flag, STGI and CLGI Instructions" on page 31)

- Intercepts—allow the VMM to intercept sensitive operations in the guest. ("Intercept Operation" on page 13 through "Miscellaneous Intercepts" on page 28)

- Interrupt and APIC assists—physical interrupt intercepts, virtual interrupt support, APIC.TPR virtualization. ("Global Interrupt Flag, STGI and CLGI Instructions" on page 31 and "Interrupt and localAPIC Support" on page 35)

- SMM intercepts and assists ("SMM Support" on page 40)

- External (DMA) access protection ("External Access Protection" on page 43)

- Nested paging support for two levels of address translation.

("Nested Paging Facility" on page 52)

- Security—SKINIT instruction, automatic memory clear. ("Secure Startup with SKINIT" on page 61)

## 2.1 Enabling SVM

Before any SVM instruction (VMRUN, VMLOAD, VMSAVE, VMMCALL, STGI, CLGI, SKINIT, INVLPGA) can be used, EFER.SVME (bit 12 of the EFER MSR register) must be set to 1. While EFER.SVME is zero (the default after reset), SVM instructions cause #UD faults.

### 2.2 VMRUN Instruction

The VMRUN instruction is the cornerstone of SVM. VMRUN takes, as a single argument, the physical address of a 4KB-aligned page, the *virtual machine control block* (VMCB), which describes a virtual machine (guest) to be executed. The VMCB contains:

- a list of which instructions or events in the guest (e.g., write to CR3) to intercept,

- various control bits that specify the execution environment of the guest or that indicate special actions to be taken before running guest code, and

- guest processor state (such as control registers, etc.).

#### 2.2.1 Basic Operation

The VMRUN instruction has an implicit addressing mode of [rAX]. Software must load RAX (EAX in 32-bit mode) with the *physical* address of the VMCB, a 4-Kbyte-aligned page that describes a virtual machine to be executed. The portion of RAX used in forming the address is determined by the current effective address size.

The VMCB is accessed by physical address and should be mapped as writeback (WB) memory.

VMRUN is available only at CPL-0 (a #GP exception is raised if the CPL is greater than 0). Furthermore, the processor must be in protected mode and SVME.EFER must be set to 1 (otherwise, a #UD exception is raised).

The VMRUN instruction saves some host processor state information in the *host state save area* in main memory at the physical address specified in the VM\_HSAVE\_AREA MSR; it then loads corresponding guest state from the VMCB state-save area. VMRUN also reads additional control bits from the VMCB that allow the VMM to flush the guest TLB, inject virtual interrupts into the guest, etc.

The VMRUN instruction then checks the guest state just loaded. If illegal state has been loaded, the processor exits back to the host (see "#VMEXIT" on page 12).

Otherwise, the processor now runs the guest code until an *intercept* event occurs, at which point the processor suspends guest execution and resumes host execution at the instruction following the VMRUN. This is called a #VMEXIT and is described in detail in "#VMEXIT" on page 12.

VMRUN saves or restores a minimal amount of state information to allow the VMM to resume execution after a guest has exited. This allows the VMM to handle simple intercept conditions quickly. If additional guest state information must be saved or restored (e.g., to handle more complex intercepts or to switch to a different guest), the VMM

can employ the VMSAVE and VMLOAD instructions (see "VMSAVE and VMLOAD Instructions" on page 29).

**Saving Host State.** To assure that the host can resume operation after #VMEXIT, VMRUN saves at least the following host state information at the physical address specified in the new MSR, VM\_HSAVE\_PA:

- CS.SEL, NEXT\_RIP—The CS selector and RIP of the instruction following the VMRUN. On #VMEXIT the host resumes running at this address.

- RFLAGS, RAX—Host processor mode and the register used by VMRUN to address the VMCB.

- SS.SEL, RSP—Host's stack pointer.

- CR0, CR3, CR4, EFER—Host's paging/operating mode.

- IDTR, GDTR—The pseudo-descriptors. (VMRUN does not save or restore the host LDTR.)

- ES.SEL and DS.SEL.

Processor implementations may store only part (or none) of host state in the memory area pointed to by VM\_HSAVE\_AREA and may store some or all host state in hidden on-chip memory. Different implementations may choose to save the hidden parts of the host's segment registers as well as the selectors. For these reasons, software must not rely on the format or contents of the host state save area, nor attempt to change host state by modifying the contents of the host save area.

**Loading Guest State.** After saving host state, VMRUN loads the following guest state from the VMCB:

- CS, RIP—Guest begins execution at this address. The hidden state of the CS segment register is also loaded from the VMCB.

- RFLAGS, RAX.

- SS, RSP—Includes the hidden state of the SS segment register.

- CR0, CR2, CR3, CR4, EFER—Guest paging mode. Writing paging-related control registers with VMRUN does *not* flush the TLB (since address spaces are switched).

- INTERRUPT\_SHADOW—This flag indicates whether the guest is currently in an interrupt lockout shadow; see "Interrupt Shadows" on page 36.

- IDTR, GDTR.

- ES and DS—Includes the hidden state of the segment registers.

- DR7 and DR6—The guest's breakpoint state.

- V\_TPR—The guest's virtual TPR.

- V\_IRQ—The flag indicating whether a virtual interrupt is pending in the guest.

- CPL—If the guest is in real mode, the CPL is forced to 0; if the guest is in v86 mode, the CPL is forced to 3. Otherwise, the CPL saved in the VMCB is used.

The processor checks the loaded guest state for consistency. If an illegal mode is detected or an exception was encountered while loading guest state, the processor performs a #VMEXIT immediately and stores VMEXIT\_INVALID as an error indication in the VMCB EXITCODE field.

If the guest is in PAE paging mode according to the registers just loaded, the processor will also read the four PDPEs pointed to by the newly loaded CR3 value; setting any reserved bits in the PDPEs also causes a #VMEXIT.

It is possible for the VMRUN instruction to load a guest RIP that is outside the limit of the guest's code segment or that is non-canonical (if running in long mode). If this occurs, a #GP fault is delivered *inside* the guest; the RIP falling outside the limit of the guest's code segment is not considered illegal guest state.

After all guest state is loaded, and intercepts and other control bits are set up, the processor reenables interrupts by setting GIF to 1. (It is assumed that VMM software cleared GIF some time before executing the VMRUN instruction, to ensure an atomic state switch).

**Control Bits.** Besides loading guest state, the VMRUN instruction reads various control fields from the VMCB; most of these fields are not written back to the VMCB on #VMEXIT (since they cannot change during guest execution):

■ TSC\_OFFSET—an offset to add when the guest reads the TSC (time stamp counter). Guest writes to the TSC can be intercepted and emulated by changing the offset (without writing the physical TSC). This offset is cleared when the guest exits back to the host.

- V\_INTR\_PRIO, V\_INTR\_VECTOR, V\_IGN\_TPR—fields used to describe a virtual interrupt for the guest (see "Injecting Virtual (INTR) Interrupts" on page 36).

- V\_INTR\_MASKING—controls whether masking of interrupts (in EFLAGS.IF and TPR) is to be virtualized (see Section 2.17 on page 35).

- The address space ID (ASID) to use while running the guest. (See Appendix B, "Processor Feature Identification," on page 91 for feature identification, including how many ASIDs are implemented.)

- A field to control flushing of the TLB during a VMRUN (see Section 2.12).

- The intercept vector describing the active intercepts for the guest. On exit from the guest, the internal intercept registers are cleared so no host operations will be intercepted.

**Segment State in the VMCB.** The segment registers are stored in the VMCB in a format similar to that for SMM: both base and limit are fully expanded; segment attributes are stored as 12-bit values formed by the concatenation of bits 55–52 and 47–40 from the original 64-bit (in-memory) segment descriptors; the descriptor "P" bit is used to signal NULL segments (P==0) where permissible and/or relevant. When loaded from the VMCB, only some of the attribute bits are observed by hardware, depending on the segment register in question:

- CS—D, L, R (null code segment are not allowed).

- SS—B, P, DPL, E, W (null stack segments allowed in 64-bit mode only).

- DS, ES, FS, GS —D, P, DPL, E, W, Code/Data.

- LDTR—Only the P bit is observed.

- TR—Only TSS type (32 or 16 bit) is relevant, since a null TSS is not allowed.

The VMM should follow these rules when storing segment attributes into the VMCB:

- For NULL segments, set all attribute bits to zero.

- Otherwise, write the concatenation of bits [55–52] and [47–40] from the original 64-bit (in-memory) segment descriptors.

- The processor reads the current privilege level from the CPL field in the VMCB, not from SS.DPL. However, SS.DPL should match the CPL field.

- When in virtual x86 or real mode, the processor ignores the CPL field in the VMCB (and forces the values of 3 and 0, respectively).

When examining segment attributes after a #VMEXIT:

- Test the Present (P) bit to check whether a segment is NULL; note that CS and TR never contain NULL segments and so their P bit is meaningless;

- Retrieve the CPL from the CPL field in the VMCB, not from any segment DPL.

Canonicalization and Consistency Checks. The VMRUN instruction performs consistency checks on host and guest state, very much like RSM performs checks on the new state. Illegal guest state combinations cause a #VMEXIT with error code of VMEXIT\_INVALID. The following conditions are considered illegal state combinations:

- EFER.SVME is zero.

- CR0.CD is zero and CR0.NW is set.

- CR0[63–32] are not zero.

- Any MBZ bits of CR3 are set.

- CR4[63–11] are not zero.

- DR6[63–32] are not zero.

- DR7[63–32] are not zero.

- EFER[63–15] are not zero.

- EFER.LMA or EFER.LME is non-zero and this processor does not support long mode.

- EFER.LME and CR0.PG are both set and CR4.PAE is zero.

- EFER.LME and CR0.PG are both non-zero and CR0.PE is zero.

- EFER.LME, CR0.PG, CR4.PAE, CS.L, and CS.D are all non-zero.

- The VMRUN or SMI intercept bits are clear.

- The SMI intercept bit is zero.

- (Other MBZ bits exist in various registers stored in the VMCB.)

- The MSR or IOIO intercept tables extend to a physical address ≥ the maximum supported physical address

- Illegal event injection (see Section 2.16 on page 33).

VMRUN can load a guest value of CR0 with PE = 0 but PG = 1, a combination that is otherwise illegal (see Section 2.15).

In addition to consistency checks, VMRUN and #VMEXIT canonicalize (i.e., sign-extend to 63 bits) all base addresses in the segment registers that have been loaded.

VMRUN and TF/RF bits in EFLAGS. When considering interactions of VMRUN with the TF and RF bits in EFLAGS, one must distinguish between the behavior of host as opposed to that of the guest.

From the host point of view, VMRUN acts like a single instruction, even though an arbitrary number of guest instructions may execute before a #VMEXIT effectively completes the VMRUN. As a single host instruction, VMRUN interacts with EFLAGS.RF and EFLAGS.TF like ordinary instructions. EFLAGS.RF suppresses any potential instruction breakpoint match on the VMRUN, and EFLAGS.TF causes a #DB trap after the VMRUN completes on the host side (i.e., after the #VMEXIT from the guest). As with any normal instruction, completion of the VMRUN instruction clears the host EFLAGS.RF bit.

The first guest instruction obeys the value of EFLAGS.RF from the VMCB. When VMRUN loads a guest value of 1 for EFLAGS.RF, that value takes effect and suppresses any potential (guest) instruction breakpoint on the first guest instruction. When VMRUN loads a guest value of 1 in EFLAGS.TF, that value does *not* cause a trace trap between the VMRUN and the first guest instruction, but rather *after* completion of the first guest instruction.

Host values of EFLAGS have no effect on the guest and guest values of EFLAGS have no effect on the host.

See also Section 2.4.1 on page 14 regarding the value of EFLAGS.RF saved on #VMEXIT.

#### 2.3 #VMEXIT

When an intercept triggers, the processor performs a #VMEXIT (i.e., an exit from the guest to the host context).

On #VMEXIT, the processor:

- Disables interrupts by clearing the GIF, so that after the #VMEXIT, VMM software can complete the state switch atomically.

- Writes back to the VMCB the current guest state—the same subset of processor state as is loaded by the VMRUN instruction, including the V\_IRQ, V\_TPR, and the INTERRUPT\_SHADOW bits.

- Saves the reason for exiting the guest in the VMCB's EXITCODE field; additional information may be saved in the EXITINFO1 or EXITINFO2 fields, depending on the intercept.

- Clears all intercepts.

- Resets the current ASID register to zero (host ASID).

- Clears the V\_IRQ and V\_INTR\_MASKING bits inside the processor.

- Clears the TSC\_OFFSET inside the processor.

- Reloads the host state previously saved by the VMRUN instruction.

Note: The processor reloads the host's CS, SS, DS, and ES segment registers and, if required, re-reads the descriptors from the host's segment descriptor tables, depending on the implementation. Software should keep the host's segment descriptor tables consistent with the segment registers when executing VMRUN instructions. Immediately after #VMEXIT, the processor still contains the guest value for LDTR. So for CS, SS, DS, and ES, the VMM must only use segment descriptors from the global descriptor table. Any exception encountered while reloading the host segments causes a shutdown.

- If the host is in PAE mode, the processor reloads the host's PDPEs from the page table indicated by the host's CR3.. If the PDPEs contain illegal state, the processor shuts down.

- Forces CR0.PE = 1, RFLAGS.VM = 0.

- Sets the host CPL to zero.

- Disables all breakpoints in the host DR7 register.

- Checks the reloaded host state for consistency; any error causes the processor to shutdown. If the host's RIP reloaded by #VMEXIT is outside the limit of the host's code segment or non-canonical (in the case of long mode), a #GP fault is delivered inside the host.

Note: When loading segment bases from the VMCB or the hostsave area (on VMRUN or #VMEXIT), segment bases are canonicalized (i.e., sign-extended from the highest implemented address bit to bit 63); see the AMD64 Architecture Programmer's Manual, Volume 2: System Programming, order# 24593.

Any illegal state or exception encountered while reloading host segment state in the VMCB state will cause a processor shutdown.

#### 2.4 Intercept Operation

Various instructions and events (such as exceptions) in the guest can be *intercepted* by means of control bits in the VMCB. The two primary classes of intercepts supported by SVM are *instruction* and *exception* intercepts.

**Exception intercepts.** Exception intercepts are checked when normal instruction processing must raise an exception—*before* resolving possible double-fault conditions according to table 8-3 in Volume 2 of the *AMD64 Architecture Programmer's Manual*, order# 24593, and before attempting delivery of the exception (which includes pushing an exception frame, accessing the IDT, etc.).

For some exceptions, the processor still writes certain exception-specific registers even if the exception is intercepted. (See the descriptions in Section 2.8 on page 23 and following for details.) When an external or virtual interrupt is intercepted, the interrupt is left pending.

When an intercept occurs while the guest is in the process of delivering a non-intercepted interrupt or exception using the IDT, SVM provides additional information on #VMEXIT (See Section 2.4.2 on page 14).

**Instruction intercepts.** These occur at well-defined points in instruction execution—before the results of the instruction are committed, but ordered in an intercept-specific priority relative to the instruction's exception checks. Generally, instruction intercepts are checked after simple exceptions (such as #GP when CPL is incorrect, or #UD) have been checked, but before exceptions related to memory accesses (such as page faults) and exceptions based on specific operand values. There are several exceptions to this guideline, e.g., the RSM instruction. Instruction breakpoints for the current instruction and pending data breakpoint traps from the previous instruction are designed to be checked before instruction intercepts.

### 2.4.1 State Saved on Exit

When triggered, intercepts write an EXITCODE into the VMCB identifying the cause of the intercept. The EXITINTINFO field signals whether the intercept occurred while the guest was attempting to deliver an interrupt or exception through the IDT; a VMM can use this information to transparently complete the delivery (see "Event Injection" on page 33). Some intercepts provide additional information in the EXITINFO1 and EXITINFO2 fields in the VMCB; see the individual intercept descriptions for details.

The guest state saved in the VMCB is the processor state as of the moment the intercept triggers. In the x86 architecture, traps (as opposed to faults) are detected and delivered *after* the instruction that triggered them has completed execution. Accordingly, a trap intercept takes place after the execution of the instruction that triggered the trap in the first place. The saved guest state thus includes the effects of executing that instruction.

**Example:** Assume a guest instruction triggers a data breakpoint (#DB) trap which is in turn intercepted. The VMCB records the guest state after execution of that instruction, so that the saved CS:RIP points at the following instruction, and the saved DR7 includes the effects of hitting the data breakpoint.

Some exceptions write special registers even when they are intercepted; see the individual descriptions in "Exception Intercepts" on page 23 for details.

# 2.4.2 Intercepts During IDT Interrupt Delivery

It is possible for an intercept to occur while the guest is attempting to deliver an exception or interrupt through the IDT e.g., #PF because the VMM has paged out the guest's exception stack). In some cases, such an intercept can result in the loss of information necessary for transparent resumption of the guest. In the case of an external interrupt, for example, the processor will already have performed an interrupt acknowledge cycle with the PIC or APIC to obtain the interrupt type and vector, and the interrupt is thus no longer pending.

To recover from such situations, all intercepts indicate (in the EXITINTINFO field in the VMCB) whether they occurred during exception or interrupt delivery though the IDT. This mechanism allows the VMM to complete the intercepted interrupt delivery, even when it is no longer possible to recreate the event in question.

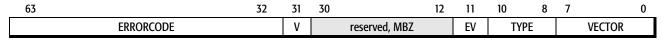

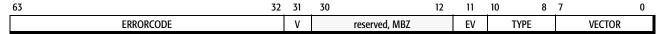

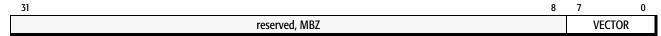

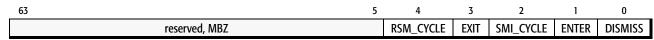

Figure 2-1. EXITINTINFO for All Intercepts

The fields in EXITINTINFO are as follows:

- VECTOR—Bits 7–0. The 8-bit IDT vector of the interrupt.

- TYPE—Bits 10–8. Qualifies the guest exception or interrupt. Table 2-1 shows possible values returned and their corresponding interrupt or exception types. Values not indicated are unused and reserved.

| Table 2-1. | Guest | Exception of | Int | errupt | Types |

|------------|-------|--------------|-----|--------|-------|

|------------|-------|--------------|-----|--------|-------|

| Value | Туре                                                    |

|-------|---------------------------------------------------------|

| 0     | External or virtual interrupt (INTR)                    |

| 2     | NMI                                                     |

| 3     | Exception (fault or trap)                               |

| 4     | Software interrupt (caused by INT <i>n</i> instruction) |

Despite the instruction name, the events raised by the INT1 (also known as ICEBP), INT3 and INTO instructions (opcodes F1h, CCh and CEh) are considered exceptions, not software interrupts. Only events raised by the INT*n* instruction (opcode CDh) are considered software interrupts.

- EV (error code valid)—Bit 11. Set to 1 if the guest exception would have pushed an error code; cleared to zero otherwise.

- V (valid)—Bit 31. Set to 1 if the intercept occurred while the guest attempted to deliver an exception through the IDT; otherwise cleared to zero.

- ERRORCODE—Bits 63–32. If EV is set to 1, holds the error code that the guest exception would have pushed; otherwise is undefined.

In the case of multiple exceptions, EXITINTINFO records the aggregate information on all exceptions but the last (and intercepted) one.

**Example:** A guest raises a #GP during delivery of which a #NP is raised (a scenario that, according to x86 rules, resolves to a #DF), and an intercepted #PF occurs during the attempt to deliver the #DF. Upon intercept of the #PF, EXITINTINFO indicates that the guest was in the process of delivering a #DF when the #PF occurred. The information about the intercepted page fault itself is encoded in the EXITCODE, EXITINFO1 and EXITINFO2 fields. If the VMM decides to repair and dismiss the #PF, it can resume guest execution by re-injecting (see "Event Injection" on page 33) the fault recorded in EXITINTINFO. If the VMM decides that the #PF should be reflected back to the guest, it must combine the event in EXITINTINFO with the intercepted exception according to x86 rules (see table 8-3 in Volume 2 of the AMD64 Architecture Programmer's Manual, order# 24593). In this case, a #DF plus a #PF would result in a triple fault or shutdown.

### 2.4.3 **EXITINTINFO Pseudo-Code**

When delivering exceptions or interrupts in a guest, the processor checks for exception intercepts and updates the value of EXITINTINFO should an intercept occur during exception delivery. The following pseudo-code outlines how the processor delivers an event (exception or interrupt) E.

```

if E is an exception and is intercepted:

#VMEXIT(E)

E = (result of combining E with any prior events)

if (result was #DF and #DF is intercepted):

#VMEXIT(#DF)

if (result was shutdown and shutdown is intercepted):

#VMEXIT(#shutdown)

EXITINTINFO = E // Record the event the guest is delivering.

```

Attempt delivery of E through the IDT Note that this may cause secondary exceptions

Once an exception has been successfully taken in the guest:

EXITINTINFO.V = 0 // Delivery succeeded; no #VMEXIT. Dispatch to first instruction of handler

When an exception triggers an intercept, the EXITCODE (and optionally EXITINFO1 and EXITINFO2) fields always reflect the (raw) intercepted exception, while EXITINTINFO (if marked valid) indicates the prior exception the guest was attempting to deliver when the intercept occurred.

#### 2.5 Instruction Intercepts

This section specifies which instructions check a given intercept and, where relevant, how the intercept is prioritized relative to exceptions.

#### 2.5.1 **Read/Write of CRO**

Checked by—MOV TO/FROM CR0, LMSW, SMSW, CLTS.

**Priority**—Checks non-memory exceptions (CPL, illegal bit combinations, etc.) before the intercept. For LMSW and SMSW, checks SVM intercepts before checking memory exceptions.

# 2.5.2 Read/Write of CR3 (excluding task switch)

**Checked by—**MOV TO/FROM CR3 (not checked by task switch operations).

**Priority**—Checks non-memory exceptions first, then the intercept. If the intercept triggers on a write, the intercept happens *before* the TLB is flushed. If PAE is enabled, the loading of the four PDPEs can cause a #GP; that exception is checked *after* the intercept check, so the VMM handling a CR3 intercept cannot rely on the PDPEs being legal; it must examine them in software if necessary.

The reads and writes of CR3 that occur in VMRUN, #VMEXIT or task switches are *not* subject to this intercept check.

# 2.5.3 Read/Write of other CRs

Checked by—MOV TO/FROM CRn.

**Priority**—All normal exception checks take precedence over the SVM intercepts.

# 2.5.4 Read/Write of Debug Registers, DRn

**Checked by**—MOV TO/FROM DR*n*. (Not checked by implicit DR6/DR7 writes.)

**Priority**—All normal exception checks take precedence over the SVM intercepts.

# 2.5.5 **Selective CR0** Write Intercept

Checked by-MOV TO CR0, LMSW

**Priority**—Checks non-memory exceptions (CPL, illegal bit combinations, etc.) before the intercept. For LMSW and SMSW, checks SVM intercepts before checking memory exceptions.

The selective write intercept on CR0 triggers only if a bit other than CR0.TS or CR0.MP is being changed by the write. In particular, this means that CLTS does not check this intercept.

When both selective and non-selective CR0-write intercepts are active at the same time, the non-selective intercept takes priority. With respect to exceptions, the priority of this intercept is the same as the generic CR0-write intercept.

The LMSW instruction treats the selective CR0-write intercept as a non-selective intercept (i.e., it intercepts regardless of the value being written).

# 2.5.6 Reading/Writing of IDTR, GDTR, LDTR, TR

Checked by—LIDT, SIDT, LGDT, SGDT, LLDT, SLDT, LTR, STR instructions, respectively.

**Priority**—The SVM intercept is checked after #UD and #GP exception checks, but before any memory access is performed.

# 2.5.7 **RDTSC Instruction Intercept**

**Checked by—**RDTSC instruction

**Priority**—Checks all exceptions before the SVM intercept.

# 2.5.8 RDPMC Instruction Intercept

Checked by—RDPMC instruction

**Priority**—Checks all exceptions before the SVM intercept.

### 2.5.9 **PUSHF Instruction Intercept**

**Checked by—**PUSHF instruction.

**Priority**—The intercept takes priority over any exceptions.

# 2.5.10 **POPF Instruction Intercept**

**Checked by—**POPF instruction.

**Priority**—The intercept takes priority over any exceptions.

# 2.5.11 **CPUID Instruction Intercept**

**Checked by—**CPUID instruction.

**Priority**—No exceptions to check.

| 2.5.12 <b>RSM</b>                   | Checked by—RSM instruction.                                                                                                                                                                    |  |  |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Instruction Intercept               | <b>Priority</b> —The intercept takes priority over any exceptions.                                                                                                                             |  |  |

| 2.5.13 <b>IRET</b>                  | Checked by—IRET instruction.                                                                                                                                                                   |  |  |

| Instruction Intercept               | <b>Priority</b> —The intercept takes priority over any exceptions.                                                                                                                             |  |  |

| 2.5.14 Software                     | Checked by—INT $n$ instruction.                                                                                                                                                                |  |  |

| Interrupt Intercept                 | <b>Priority</b> —The intercept occurs before any exceptions are checked. The CS:RIP reported on #VMEXIT are those of the intercepted INT <i>n</i> instruction.                                 |  |  |

|                                     | Though the INT $n$ instruction may dispatch through IDT vectors in the range of 0–31, those events cannot be intercepted by means of exception intercepts ("Exception Intercepts" on page 23). |  |  |

| 2.5.15 <b>INVD</b>                  | Checked by—INVD instruction.                                                                                                                                                                   |  |  |

| Instruction Intercept               | <b>Priority</b> —Exceptions (#GP) are checked before the intercept.                                                                                                                            |  |  |

| 2.5.16 <b>PAUSE</b>                 | Checked by—PAUSE instruction (opcode F3 90).                                                                                                                                                   |  |  |

| Instruction Intercept               | Priority—No exceptions to check.                                                                                                                                                               |  |  |

| 2.5.17 HLT Instruction<br>Intercept | Checked by—HLT instruction.                                                                                                                                                                    |  |  |

|                                     | <b>Priority</b> —Checks all exceptions before checking for this intercept.                                                                                                                     |  |  |

| 2.5.18 INVLPG                       | Checked by—INVLPG instruction.                                                                                                                                                                 |  |  |

| Instruction Intercept               | <b>Priority</b> —Checks all exceptions (#GP) before the intercept.                                                                                                                             |  |  |

| 2.5.19 INVLPGA                      | Checked by—INVLPGA instruction.                                                                                                                                                                |  |  |

| Instruction Intercept               | <b>Priority</b> —Checks all exceptions (#GP) before the intercept.                                                                                                                             |  |  |

| 2.5.20 <b>VMRUN</b>                 | Checked by—VMRUN instruction.                                                                                                                                                                  |  |  |

| Instruction Intercept               | <b>Priority</b> —Checks exceptions (#GP) before the intercept.                                                                                                                                 |  |  |

|                                     | Note: The VMRUN intercept must always be set in the VMCB.                                                                                                                                      |  |  |

| 2.5.21 VMLOAD                       | Checked by—VMLOAD instruction.                                                                                                                                                                 |  |  |

| Instruction Intercept               | <b>Priority</b> —Checks exceptions (#GP) before the intercept.                                                                                                                                 |  |  |

**Priority**—Checks exceptions (#GP) before the intercept.

| 2.5.22 VMSAVE<br>Instruction Intercept | Checked by—VMSAVE instruction.                                                                                           |  |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|

|                                        | <b>Priority</b> —Checks exceptions (#GP) before the intercept.                                                           |  |

| 2.5.23 VMMCALL                         | Checked by—VMMCALL instruction.                                                                                          |  |

| Instruction Intercept                  | <b>Priority</b> —The intercept takes priority over exceptions. VMMCALL causes #UD in the guest if it is not intercepted. |  |

| 2.5.24 <b>STGI</b>                     | Checked by—STGI instruction.                                                                                             |  |

| Instruction Intercept                  | <b>Priority</b> —Checks exceptions (#GP) before the intercept.                                                           |  |

| 2.5.25 <b>CLGI</b>                     | Checked by—CLGI instruction.                                                                                             |  |

| Instruction Intercept                  | <b>Priority</b> —Checks exceptions (#GP) before the intercept.                                                           |  |

| 2.5.26 <b>SKINIT</b>                   | Checked by—SKINIT instruction.                                                                                           |  |

| Instruction Intercept                  | <b>Priority</b> —Checks exceptions (#GP) before the intercept.                                                           |  |

| 2.5.27 <b>RDTSCP</b>                   | Checked by—RDTSCP instruction.                                                                                           |  |

| Instruction Intercept                  | <b>Priority</b> —Checks all exceptions before the SVM intercept.                                                         |  |

| 2.5.28 <b>ICEBP</b>                    | Checked by—ICEBP instruction (opcode F1h).                                                                               |  |

| Instruction Intercept                  | Note: Although the ICEBP instruction dispatches through IDT vector 1, that event is not interceptable by means of the    |  |

2.5.29 **WBINVD Instruction Intercept**

Checked by—WBINVD instructions.

#DB exception intercept.

**Priority**—Checks exceptions (#GP) before the intercept.

#### 2.6 IOIO Intercepts

The VMM can intercept IOIO instructions (IN, OUT, INS, OUTS) on a port-by-port basis by means of the SVM I/O permissions map.

**I/O Permissions Map.** The I/O Permissions Map (IOPM) occupies 12 Kbytes of *contiguous physical* memory. The table is structured as a linear array of 64K+3 bits (two 4-Kbyte pages, and the first three bits of a third 4-Kbyte page) and must be aligned on a 4-Kbyte boundary; the *physical* base address of the IOPM is specified in the IOPM\_BASE\_PA field in the VMCB and loaded into the processor by the VMRUN instruction.

Note: The VMRUN instruction ignores the lower 12 bits of the address specified in the VMCB. If the address of the last byte in the table is greater than or equal to the maximum supported physical address, this is treated as illegal VMCB state and causes a #VMEXIT(VMEXIT\_INVALID).

Each bit in the table corresponds to an 8-bit I/O port. Bit 0 in the table corresponds to I/O port 0, bit 1 to I/O port 1 and so on. A bit set to 1 indicates that accesses to the corresponding port should be intercepted. The IOPM is accessed by physical address, and should reside in memory that is mapped as writeback (WB).

**IN and OUT Behavior.** If the IOIO\_PROT intercept bit is set, the IOPM table controls port access. For IN/OUT instructions that access more than a single byte, the permission bits for all bytes are checked; if any bit is set to 1, the I/O operation is intercepted.

Exceptions related to virtual x86 mode, IOPL, or the TSS-bitmap are checked *before* the SVM intercept check. All other exceptions are checked *after* the SVM intercept check.

**I/O Intercept Information.** When an IOIO intercept triggers, the following information (describing the intercepted operation in order to facilitate emulation) is saved in the VMCB's EXITINFO1 field:

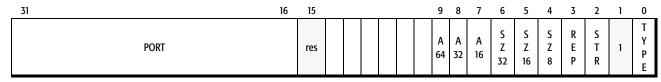

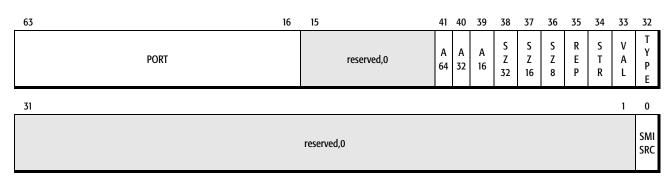

Figure 2-2. EXITINFO1 for IOIO Intercept

The fields are as follows:

- PORT—Intercepted I/O port

- A64—64-bit address size

- A32—32-bit address size

- A16—16-bit address size

- SZ32—32-bit operand size

- SZ16—16-bit operand size

- SZ8—8-bit operand size

- REP—Repeated port access

- STR—String based port access (INS, OUTS)

- TYPE—Access type (0 = OUT instruction, 1 = IN instruction)

The RIP of the instruction *following* the IN/OUT is saved in EXITINFO2, so that the VMM can easily resume the guest after I/O emulation.

#### 2.7 MSR Intercepts

The VMM can intercept RDMSR and WRMSR instructions by means of the *SVM MSR permissions map* (MSRPM) on a per-MSR basis.

MSR Permissions Map. The MSR permissions bitmap consists of a number of smaller separate bitmaps of 2K bytes each covering a defined range of 8K MSRs. Four of these smaller bitmaps reside in two physical pages (8KB, covering 32K MSRs). One 8Kbyte range is used for the Pentium® compatible MSRs, the next 8K range is used for the AMD sixth generation x86 processor (AMD-K6®) MSRs, and the third 8K range for the AMD seventh and eighth generation x86 processors (e.g., the AMD Athlon<sup>TM</sup> and AMD Opteron<sup>TM</sup>) MSRs. If the MSR\_PROT intercept is active, any attempt to read or write an MSR not covered by the bitmap will automatically cause an intercept.

The MSRPM is accessed by physical address, and should reside in memory that is mapped as writeback (WB). The MSRPM must be aligned on a 4KB boundary. The physical base address of the MSRPM is specified in MSRPM\_BASE\_PA field in the VMCB and loaded into the processor by the VMRUN instruction.

Note: The VMRUN instruction ignores the lower 12 bits of the address specified in the VMCB, and if the address of the last byte in the table is greater than or equal to the maximum supported physical address, this is treated as illegal VMCB state and causes a #VMEXIT(VMEXIT\_INVALID).

| Byte Offset | MSR Range             | Current Usage                                          |

|-------------|-----------------------|--------------------------------------------------------|